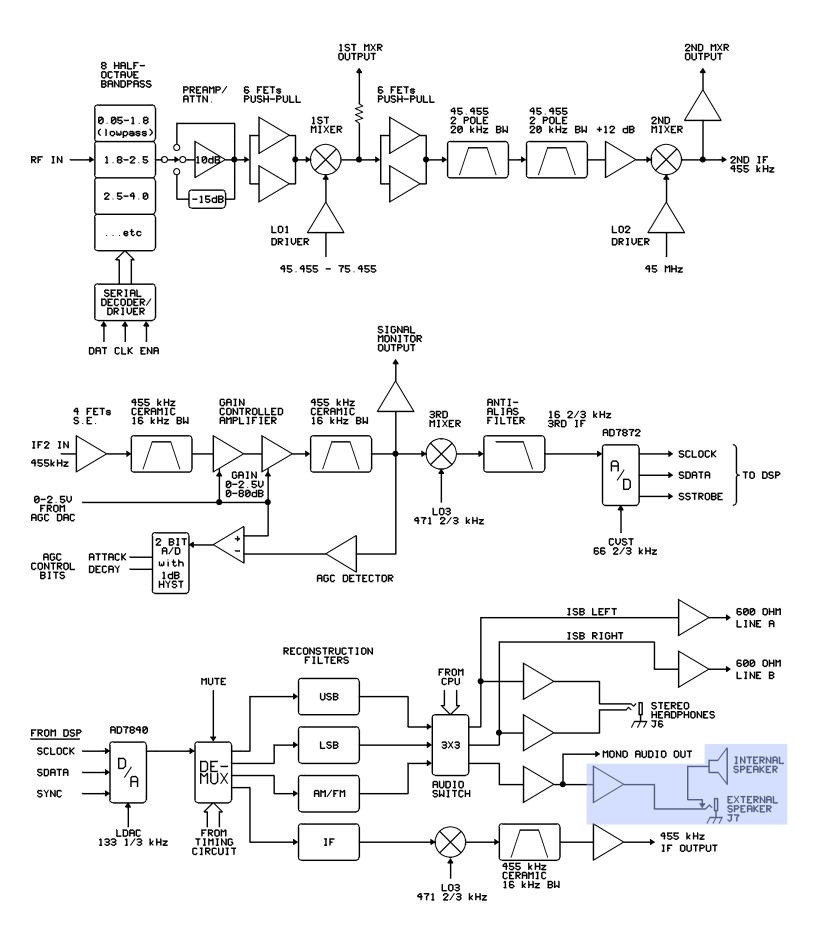

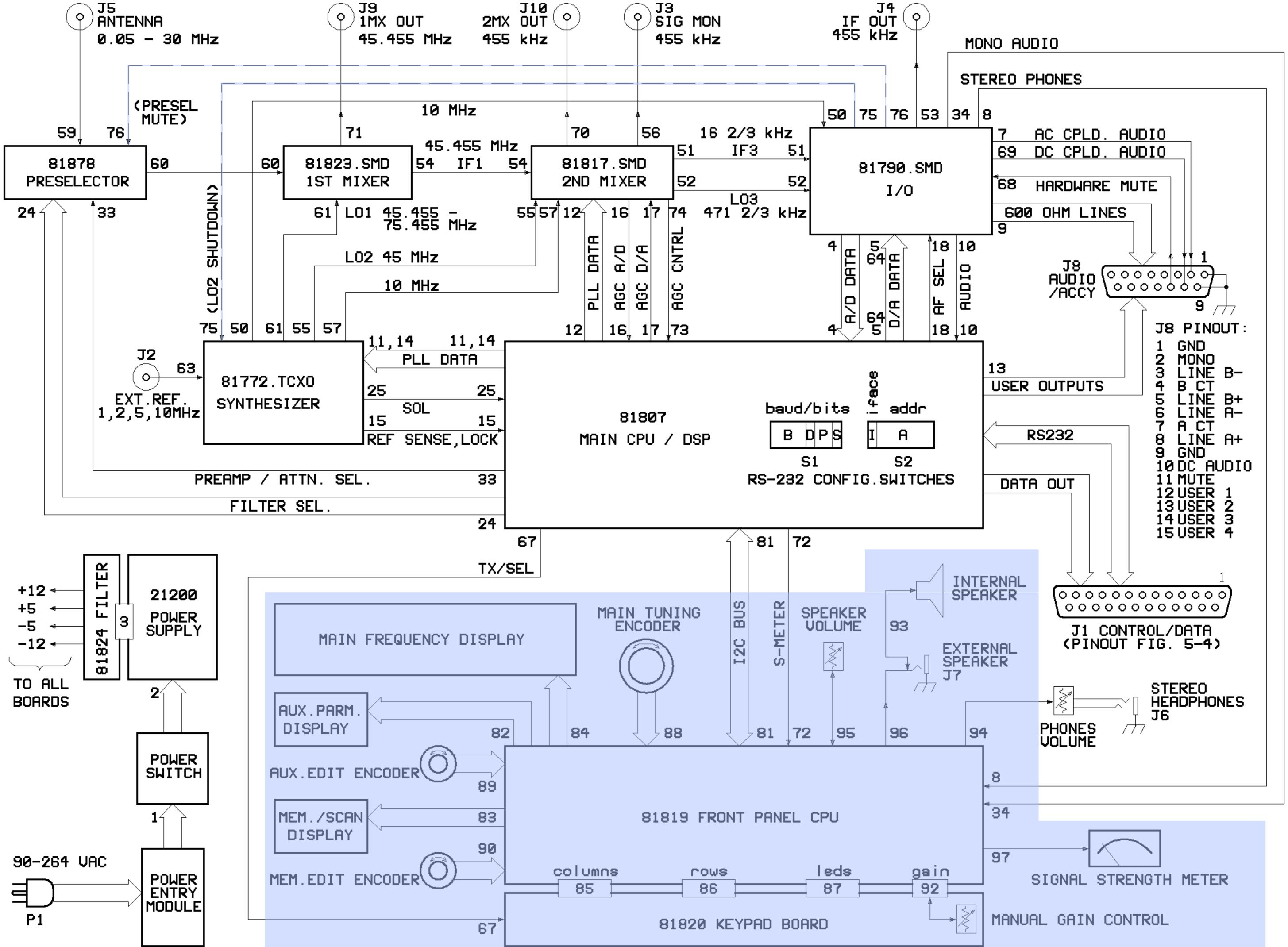

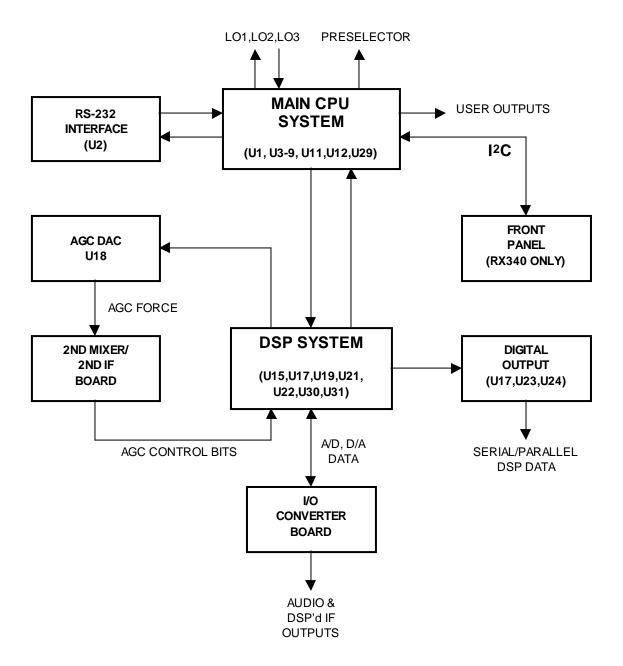

## **MODEL RX-340 BLOCK DIAGRAM**

## Technical Description of the RX331/340 analog AGC System

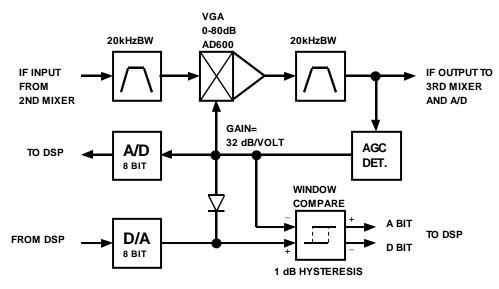

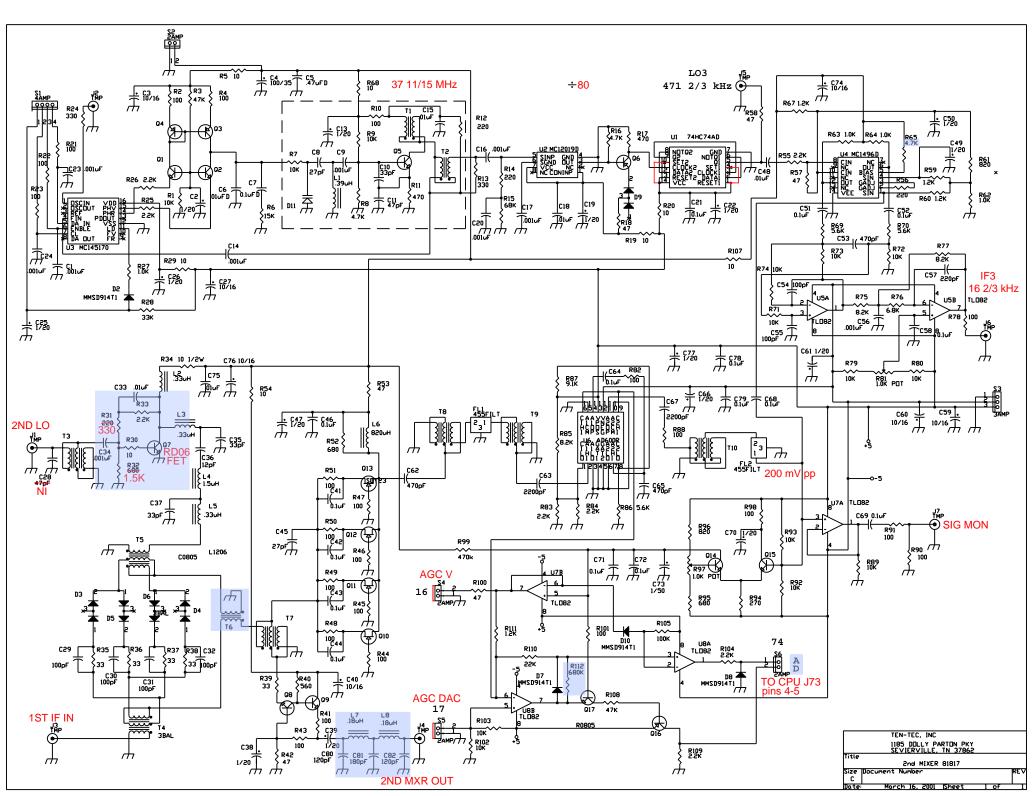

The 455 kHz analog IF amplifier provides most of the receiver's gain. The IF bandwidth is 20 kHz and an analog AGC loop with a fast natural time constant levels the IF amplifier's output to about 200 mV peak-to-peak over an 80 dB input range. The onset of this analog AGC is about 60 dB above the receiver's noise floor. The main purpose of this AGC loop is to protect the A/D converter from overload from strong signals. Weaker signal AGC is accomplished in the DSP (digital AGC) after the narrow bandwidth selectivity filtering.

The analog AGC needs to be overridden (set to lower gain) by the DSP in two cases, discussed below. The analog AGC also needs to be monitored by the DSP so it can make some fast gain corrections to the digital AGC. These digital gain corrections will be discussed after the two analog override cases.

First, when a medium or slow AGC decay rate is selected, the IF gain must return (after an analog AGC attack) at a controlled, slower than natural rate. This slower decay rate is necessary in cases such as SSB or low frequency AM modulation to prevent the fast analog AGC from "washing out" the modulation envelope. Also, this decay rate must be coordinated with the DSP's independent digital AGC to prevent a "double decay rate" phenomenon.

Second, for manual setting of less-than-maximum receiver gains, the analog AGC voltage must be overridden by a fixed voltage "ceiling" to place an upper bound on IF gain. For manual gain reduction, the digital gain is reduced first, and then the analog gain is reduced – preserving system noise figure at the lower gain settings.

This overriding control is accomplished with an op-amp circuit that "ORs" a D/A converter output with the naturally occurring analog AGC voltage. The op-amp circuit also develops two feedback bits that inform the DSP who is in control of the analog AGC at any instant – the analog AGC detector ("A" bit) or the D/A converter ("D" bit). These bits are used for two purposes: 1) coordination of analog and digital decay rates as mentioned in the first case above, and 2) correcting fast gain changes caused by large signals that are outside of the DSP selectivity filter passband. This second purpose is discussed below.

The operator expects AGC action only on signals that are inside the passband of the DSP selectivity filters – those signals he can "hear." These are called "in-band" signals. If a large signal exists outside the DSP passband, but inside the wider analog IF passband (the "out-of-band" signal), it will be unheard, but gain changes caused by the analog AGC action will cross-modulate the level of the in-band signal. Slow changes in gain due to this scenario will be followed (and corrected) by the DSP (digital) AGC. But a gain reduction that occurs at a rate faster than the selected AGC decay rate must be differentiated from a "real" drop in the level of the in-band signal. Left uncorrected, this artificial drop in receiver gain will punch an audible "hole" in the in-band signal until the digital AGC slowly decays to restore the signal level.

The logical differentiation between in-band and out-of-band caused gain reduction is accomplished by monitoring the "A" bit from the op-amp ORing circuit. Each time an "A" bit occurs, indicating analog AGC attack, an A/D converter on the analog AGC voltage is read and compared to the previous reading. The digital AGC is then allowed a fast decay only by the dB difference in the previous and present A/D values. This fast decay is only **allowed** and not forced, because it is only needed if the attack was caused by an out-of-band signal. If the attack was caused by the in-band signal, the "A" bit is the normal result of an increase in level of a strong desired signal, and no fast decay will be used because the in-band signal is already at (or very slightly above) the digital AGC attack threshold. As long as the "A" bit persists, the D/A is ramped down at the selected attack rate.

The "D" bit indicates that the D/A is controlling the analog AGC voltage instead of the AGC detector, and it is used to initiate a ramp-up of the D/A at the requested decay rate – simulating a decaying capacitor charge on the analog AGC line. As long as the "D" bit persists, the D/A continues ramping to its limit followed by increasing DSP gain (at the same rate) until full receiver gain is restored.

There is a 1 dB window where neither "A" nor "D" bit is expressed. This is considered the steady-state analog AGC voltage, and the D/A value is held constant. "A" and "D" bits never occur simultaneously.

Using a similar scheme in the RX400 will allow the feature of fully programmable AGC attack, hang, and decay rates in addition to improved cross-modulation performance due to the out-of-band AGC correction.

Note: The AD8367 is an improved version of the AD600 VGA, useable to 500 MHz. I would recommend placing most of the receiver gain at 21.4 MHz though, where the 300-500 kHz bandwidth would reduce the number of "out-of-band" signals.

```

RX331/340 ANALOG AGC CONTROL SYSTEM

```

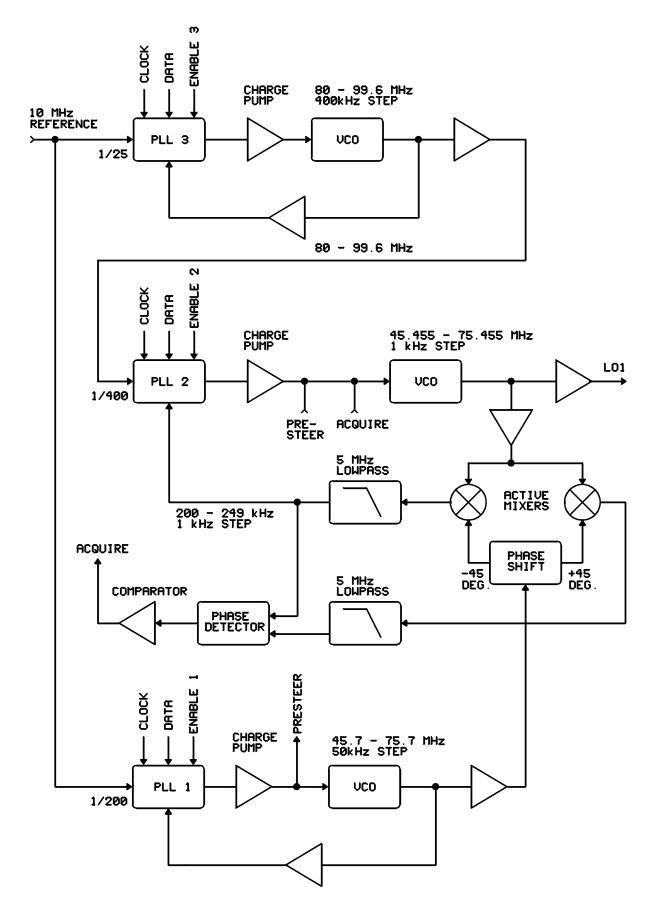

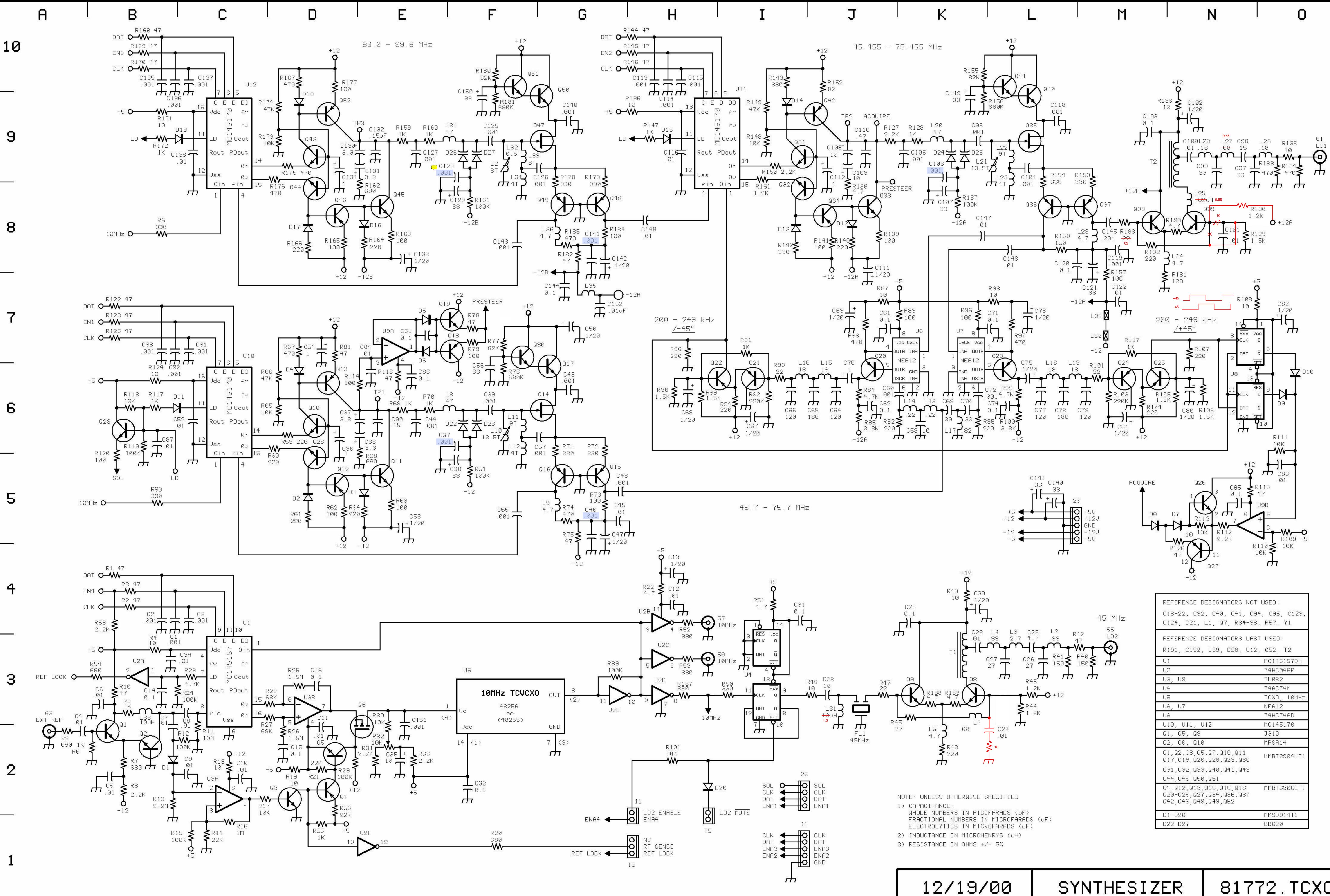

SYNTHESIZER

81772.TCXO